반도체

[디지털 회로] pipelining & blocking/non-blocking assignment

직딩 루피덕후

2023. 4. 29. 21:58

반응형

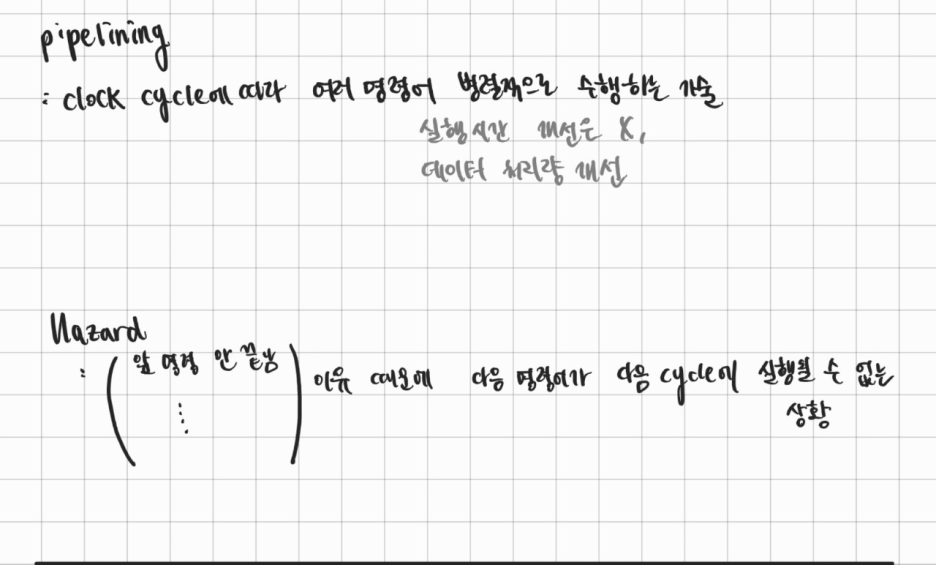

*pipelining, Hazard*

*structural hazard : 여러 instruction이 동시에 접근할 때

*data hazard : 이전 instruction이 완료되지 않아 다음 instruction 수행하는데 영향을 끼칠 때

*control hazard : instruction이 부정확해서 판단하기 어려운 경우

*pipelining on verilog*

매 pipeline stage output에 register 추가

*blocking / non-blocking assignment*

*blocking/ non blocking assignment 코딩 가이드*

-sequential logic - non blocking assignment

-combinational logic을 always 문안에 - blocking assignment

-같은 always문 안에 blocking/non-blocking assignment 혼용x -> comb+seq 둘다 쓴다면 non-blocking assignment로 통일

이미지 썸네일 삭제

[Verilog 문법] Blocking & Non Blocking에 대해 알아보자

지난 포스팅에서 wire와 reg의 올바른 사용에 대해서 살펴보았다. 해당 개념을 설명하면서, 자연스럽게 연속적 할당(continuous assignment)과 절차적 할당(procedural assignment)에 대해서 언급했었다. Verilog..

dreamsailor.tistory.com

반응형