반도체

[전자회로] MOSFET 증폭기 설계

직딩 루피덕후

2023. 4. 13. 09:06

반응형

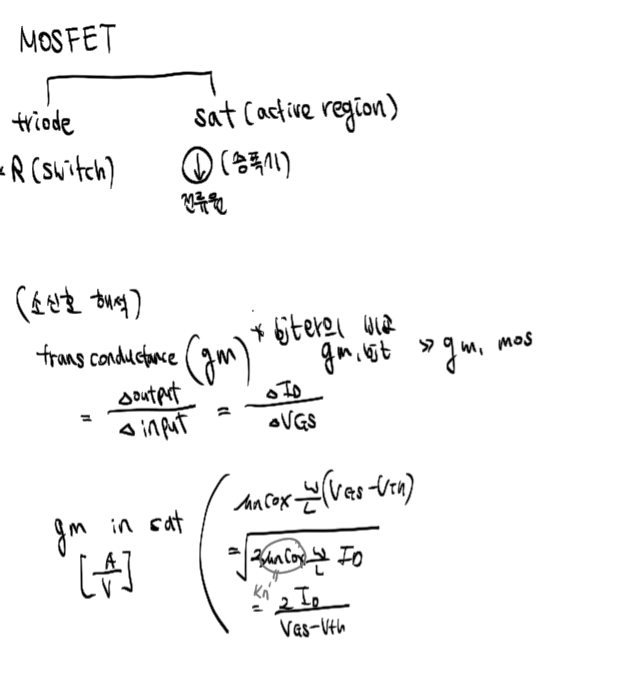

mosfet 동작 영역별 활용과 gm(transconductance)

사진 설명을 입력하세요.

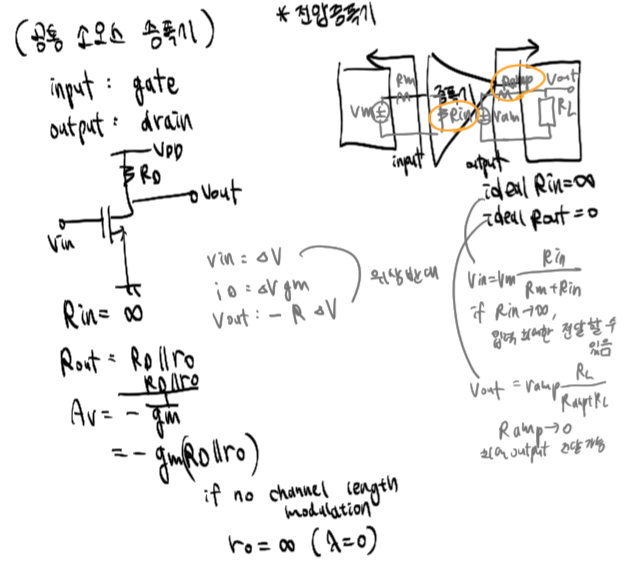

공통 소오스/공통 게이트/소오스 팔로워

(공통 소오스 증폭기)

+ 전압 증폭기의 이상적인 Rin, Rout

사진 설명을 입력하세요.

공통 소오스 증폭기 - load에 따른 성능(voltage headroom/bias 안정화/gain/Rout) 변화

current source load : bias 안정화(voltage headroom 문제 해결), gain 상승 <-> 공정 파라미터 문제로 의도와 다르게 설계될 수 있음

diode connected load : Rout, gain 감소 <->process variation 문제 완화

source degeneration : gain 감소 <-> bias 안정화

biasing circuit 과 capacitor의 활용(dc block/coupling cap)

사진 설명을 입력하세요.

(공통 게이트 증폭기)

낮은 Rin -> CS와 cascode 구조에서 활용(CS의 증폭도 유지 + 낮은 Rin= 낮은 reactance로 손실이 적어 고주파 impedance matching에 용이)

사진 설명을 입력하세요.

사진 설명을 입력하세요.

(소오스 팔로워)

Av<1, 높은 Rin과 낮은 Rout으로 이상적인 증폭기에 가까움

Av를 1에 가깝게 설계하면 버퍼역할을 하는 증폭기 설계 가능

사진 설명을 입력하세요.

반응형