| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 | 31 |

- 디램동작원리

- 차동구조

- DRAM의동작특성

- 소신호

- 디지털집적회로

- voltagedoubler

- cmosinverter

- 회로설계

- shortcircuitctransconductance

- combinational

- 반도체

- DRAM

- 따따상

- 삼성전자인턴

- nonblocking

- DRAM동작원리

- 삼성전자DS

- 따상

- 삼성전자대학생인턴

- currentmirror

- 아날로그회로설계

- 메모리반도체

- 삼성전자인턴합격

- 회로설계취준

- levelshifter

- 소신호해석

- FiniteStateMachine

- 비휘발성메모리

- 전자회로

- Flash메모리

- Today

- Total

루피덕후의 블로그

[디지털 회로] FSM/combinational & sequential logic 본문

1) combinational & sequential logic

combinational logic : 현재의 입력만 출력에 영향을 미치는 구조

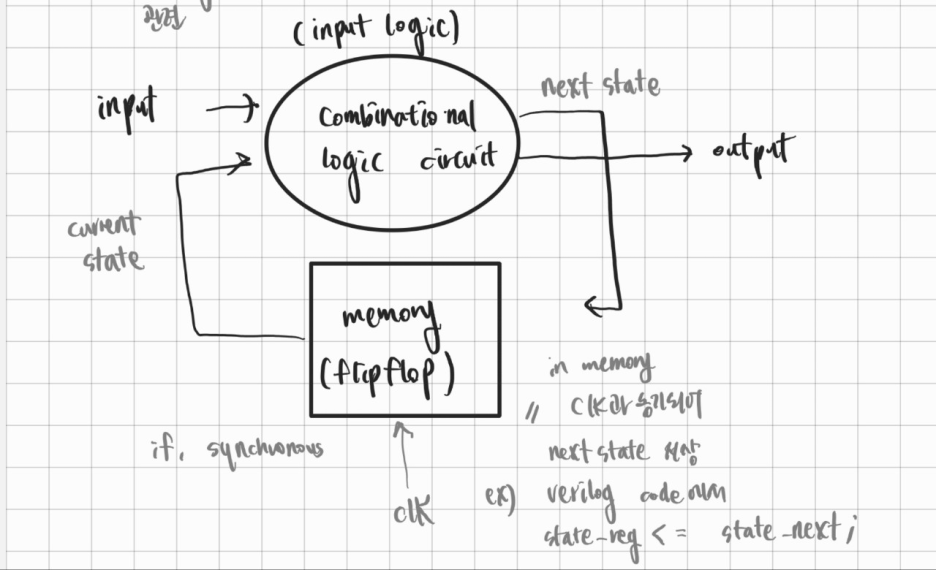

sequential logic : 현재의 입력 + 과거의 출력(memory)-현재 state이 모두 현재 출력에 영향을 미치는 구조

- synchronous : clock 하나에 의해 동기화 되는

-asynchronous : clock이 없는 or clock과 다른 신호들(ex-n_rst)을 포함해 동기화 되는

2) FSM

: state와 input이 output에 영향을 미치는 logic 구조

sequential logic내에서 combination logic circuit을 거치면 next state가 결정이 되는데 이 부분이

memory(flipflop)로 들어가 clk과 동기되어 저장되고, 그 memory에서 나온 output이 current state가 됨

input(by combinatioal logic) + state(by memory)로 output logic이 결정됨

moore machine

mealy는 여기서 input이 output logic에도 반영되도록

+ moore machine & mealy machine

*moore : 현재 state만이 output logic에 영향을 미치는 sequential logic

: output이 안정적

*mealy : input과 현재 state가 모두 output logic에 영향을 미치는 sequential logic

mealy : 설계의 어려움

: 시간지연 발생

*verilog code로 구현한 sequential logic & combinational logic

*sequential logic :

next state로 current state를 만듦(clk이 동기화될 때) = combinational logic을 거쳐 나온 next_state를 memory(flipflop)에 저장해

이 값을 current state에 대입함

*combinational logic :

-next state 만드는 logic

-output 만드는 logic

*moore : output logic에서 always@(state)

*mealy : output logic에서 always@(state, input)

*verilog code로 구현한 FSM

//state transition logic

(negedge rst_n일 때 초기화 or posedge clk일 때) next_state를 current_state에 대입

//combinational logic - next state 결정

(state나 input이 바뀔 때) case문에 따라 state가 달라질 때 if(input이 ??이면) next state가 바뀌는 구조

//output logic

state에 의해서만 output 결정되면 moore

input, state가 동시에 output 결정하면 mealy

'반도체' 카테고리의 다른 글

| [디지털 회로] pipelining & blocking/non-blocking assignment (0) | 2023.04.29 |

|---|---|

| [디지털 회로] latch & flipflop (0) | 2023.04.29 |

| [메모리 반도체]SRAM의 구조와 동작원리 (0) | 2023.04.29 |

| SLC,MLC,TLC 비교 (속도,단위 면적당 비트 용량, 수명) (0) | 2023.04.19 |

| [메모리 반도체]Flash Memory (0) | 2023.04.19 |