| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- DRAM의동작특성

- 아날로그회로설계

- 따상

- 전자회로

- 비휘발성메모리

- 삼성전자대학생인턴

- 소신호

- nonblocking

- 반도체

- 차동구조

- 삼성전자인턴합격

- 따따상

- 회로설계취준

- Flash메모리

- FiniteStateMachine

- voltagedoubler

- 회로설계

- 소신호해석

- shortcircuitctransconductance

- cmosinverter

- DRAM동작원리

- 삼성전자DS

- 디램동작원리

- 삼성전자인턴

- 메모리반도체

- levelshifter

- currentmirror

- combinational

- DRAM

- 디지털집적회로

- Today

- Total

루피덕후의 블로그

[메모리 반도체]Flash Memory 본문

비휘발성 메모리

: 전원이 꺼져도 데이터 보존

*FLASH

: control gate와 substrate사이에 floating gate 존재

*NOR Flash와 NAND Flash의 비교

|

|

NOR flash

|

NAND Flash

|

|

특징

|

속도 빠름

bit-wise programming |

고 집적도

block-wise programming |

|

활용

|

program memory

|

data storage(USB/SSD)

|

|

program

|

hot electron

|

FN tunneling

|

|

erase

|

FN tunneling

|

FN tunneling

|

+DRAM보다 속도 느림

oxide가 망가질 수 있어 programming의 제한있음

*NOR FLASH의 program/erase 동작 수행

-hot electron effect

: V drain이 Vsource보다 높아 전류가 흐르는 상태 + 그런데 Vgate가 V drain보다 높아 gate 지점에서 전자가 floating gate로 빠져나가는 상황

*FLASH에서 '1','0'저장 여부는 floating gate에서의 전자 유무에 의해 결정되므로

이때는 floating gate에 '1'저장(program)

-FN tunneling effect

: source와 drain이 floating 상태이고, Vbody>Vgate이면 floating gate에 있던 전자가 sub로 빠져나옴

flating gate에 '0' 저장(erase)

*NOR FLASH의 read 동작 수행

read '1'

programmed cell에서 WL을 low로 연결/bit line에 전류가 흐르지 않아 '1'을 읽을 수 있도록

read '0'

erasedd cell에서 WL을 high로 연결/bit line에 gnd가 연결되고 '0'을 읽을 수 있도록

**이 부분(NOR FLASH의 read 동작)은 추후 다시 정리

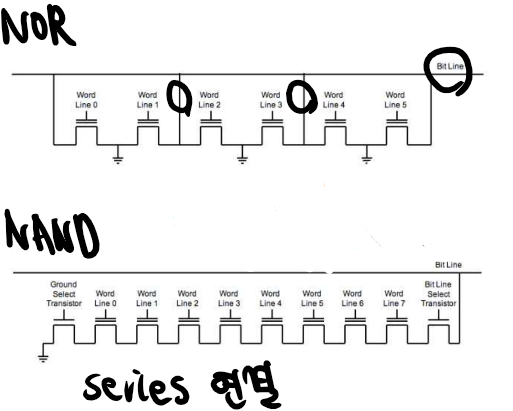

*NOR FLASH와 NAND FLASH의 회로도 차이*

CMOS NOR, CMOS NAND 회로 schematic을 생각했을 때

NMOS가 병렬연결된 것은 NOR, 직렬연결된 것은 NAND 회로

각 cell의 bit line끼리 연결 : NOR FLASH

각 cell끼리 직렬 연결 : NAND FLASH

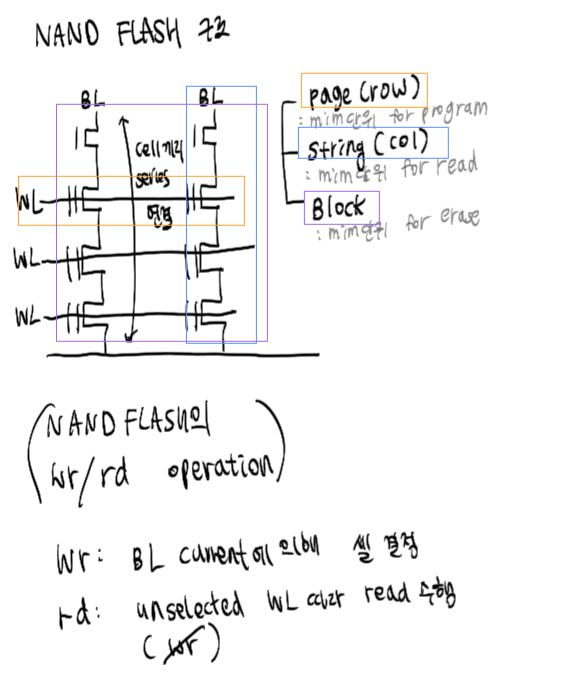

*NAND FLASH

NAND FLASH의 구조와 wr/rd 모드 수행

'반도체' 카테고리의 다른 글

| [메모리 반도체]SRAM의 구조와 동작원리 (0) | 2023.04.29 |

|---|---|

| SLC,MLC,TLC 비교 (속도,단위 면적당 비트 용량, 수명) (0) | 2023.04.19 |

| [메모리 반도체]DRAM의 wr/rd 동작 원리 (1) | 2023.04.17 |

| [메모리 반도체]NAND FLASH의 구조와 동작원리 (0) | 2023.04.17 |

| [메모리 반도체] DRAM의 구조와 동작원리 (0) | 2023.04.16 |