| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- DRAM의동작특성

- 따따상

- 삼성전자DS

- levelshifter

- 디지털집적회로

- currentmirror

- FiniteStateMachine

- DRAM동작원리

- voltagedoubler

- 삼성전자인턴

- 삼성전자대학생인턴

- 메모리반도체

- nonblocking

- shortcircuitctransconductance

- cmosinverter

- 디램동작원리

- 소신호

- 차동구조

- 반도체

- combinational

- 회로설계취준

- DRAM

- 소신호해석

- 아날로그회로설계

- 비휘발성메모리

- 회로설계

- 따상

- 삼성전자인턴합격

- Flash메모리

- 전자회로

- Today

- Total

루피덕후의 블로그

[전자회로] mosfet I-V curve/channel length modulation/short channel effect 본문

[전자회로] mosfet I-V curve/channel length modulation/short channel effect

직딩 루피덕후 2023. 4. 14. 22:11

MOSFET :

gate 전압을 가해서 channel을 형성하고, drain-source사이에 전압을 가해 전류 흐름을 제어하는 소자

전압 증폭 소자

<---> 전류 증폭 소자인 BJT

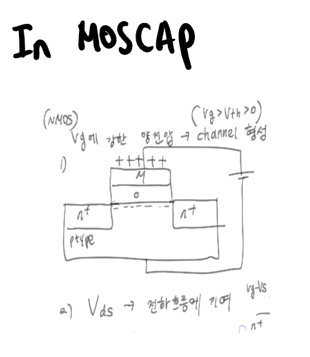

(1) MOSCAP에서의 channel 형성과 전하 흐름

가운데 절연막이 위치해있기 때문에 moscap은 capacitor처럼 동작한다고 볼 수 있다.

capacitor 한 쪽 금속판에 전압을 걸어주었을 때, 반대쪽 금속판에 전하가 유도되는 원리로 인해

NMOS기준으로 MOSCAP의 gate 단자에 양전압을 걸어주면, 그 반대극판인 p-type semiconductor에는 음의 전하가 쌓인다.

이 때, mosfet의 on/off를 결정짓는 문턱전압(Vth)보다 큰 gate 전압이 인가되면, source와 drain사이 전하가 이동할 수 있는 통로인 채널이 형성된다.

이 상태에서 drain-source 전압이 인가되면 drain에서 source방향으로 드레인 전류가 흐른다.

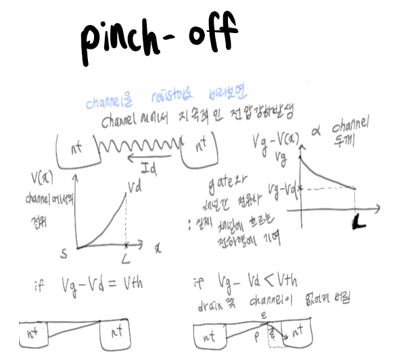

(2) pinch-off

이 때 channel을 resistor로 바라볼 수 있는데, 이 저항에의해 drain과 source사이는 지속적인 전압 강하가 발생한다.

source에서 drain쪽 방향을 x축으로 두고, channel을 형성하는데 기여하는 전압이라고 생각한다면,

channel을 형성하는데 기여하는 전압은 moscap의 양 극판 gate-channel사이 걸린 전압이므로 Vg-V(x)이고,

이 값은 drain쪽에서 Vg-Vd로 최솟값이다.

이 과정에서 Vg-Vd가 만약 Vth보다 작은 값을 취한다면, drain에 도달하기 전에 이미 채널의 끝에 도달한다.

전압이 Vth보다 작을 때는 channel이 형성되지않기 때문이다.

채널이 drain까지 형성되지 않으면, 전류가 끊기지 않나 생각할 수 도 있겠지만 p-type substrate와 drain/channel 사이 공핍층이 두껍게 형성되어 강하게 형성된 전계에 의해 channel 끝에 형성된 전류가 그대로 흐르게된다.

전류가 Vds와 무관하고 일정하다는 점에서, Vg-Vd<Vth일 때 MOSFET은 saturation region에 속하며 analog 디바이스에서 증폭기로 활용된다.

(<--->bjt는 active region에서 전류가 일정하고, saturation 영역에서 저항처럼 동작한다는 특징과 반대)

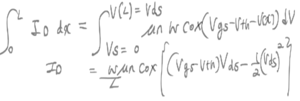

(3) mosfet의 I-V curve 수식 유도

Mosfet은 MOSCAP으로서의 동작을 포함하므로 capacitor의 capacitance 관계식 Q= CV.........(1)과

전류의 정의 I = dq/dt(단위 시간당 전하의 변화량)........(2)식을 이용해서 mosfet 전류 수식을 유도해보겠다.

from eq(1)

C(unit length gate capacitance)=WCox[f/m^2]

Q=CV=WCox*V

이 때 mosfet의 전류에 기여하는 전하량은 channel을 형성하는데 기여하는 전압의 크기와 동일하므로

Vgs-V(x),(V(x)는 x지점에서의 channel 전압)이고, transistor의 문턱전압보다는 커야하므로 V=Vgs-V(x)-Vth

from eq(2)

I=dq/dt=Q*v(v=단위 시간당 전하가 이동한 거리)

v=-un*E=undV/dx

//E방향과 전자의 이동방향은 반대이므로 음의 부호

eq(1), eq(2)의 식을 합치면

I=WCox(Vgs-Vth-V(x))*un*dV/dx

Idx=WCox(Vgs-Vth-V(x))*un*dV양변을 x=0부터 x=L까지 적분하면

mosfet의 전류식 유도

이 때 Vgs-Vth<Vds이면 Vgs-Vth=Vds일떄와 동일한 전류가 흐르므로

위의 식에서 Vds=Vgs-Vth에 대입해 전류식을 구할 수 있다

0<Vds<Vgs-Vth 인 영역은 linear영역으로 Vds가 증가할 때 이에 비례하여 Id가 증가한다.

저항으로 동작하며 digital 회로에서 스위치로 활용된다,

Vds>Vgs- Vth인 영역은 saturation영역으로 Vds와 무관하게 일정한 전류값을 가진다.

전류원으로 동작하며 analog회로에서 증폭기로 활용된다.

(4) channel length modulation

Vds>Vgs-Vth인 영역에서는 Vds가 점차 증가하면서, 전하 흐름에 기여하는 채널의 길이가 점점짧아지게 된다.

채널은 도선의 저항으로 바라볼 수 있으므로, channel의 길이가 변조되면서 전류가 증가하는 현상을 channel length modulation이라고 한다.

channel length modulation에 의해 발생하는 문제점 중 하나로, non ideal한 전류값과 동작영역을 얻을 수 있다는 것이다.

current mirror같이 전류원의 전류를 복사해서 사용할 때, channel length modulation이 발생하면 의도한 전류를 사용하지 못한다는 단점이 있다.

*channel length modulation 해결법

mosfetc scaling에 따라 소자가 미세화되면서, 집적도는 높아졌지만 short channel effect에 의해 누설전류가 발생한다는 단점이 있다.

이를 해결하기 위한 방안에는 HKMG(high k metal gate) 공정이 있으며, 높은 유전율의 capacitance를 사용함으로써 전하를 많이 가두어 누설전류를 방지할 수 있다는 장점이 있다.

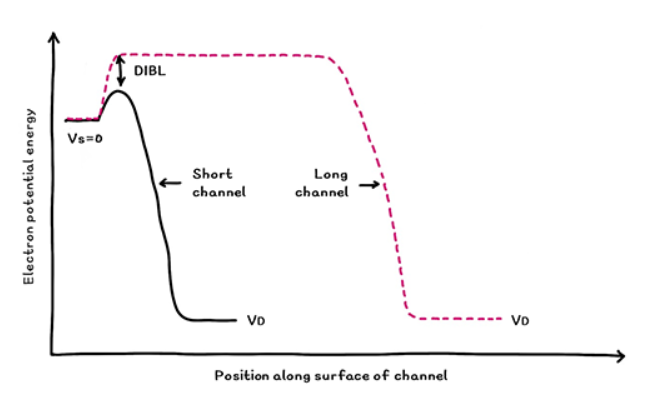

(5) short channel effect

channel이 짧아지면서 발생하는 side effect에 대해 알아보자.

1) DIBL(drain induced barrier lowering)

: drain 전압이 높아지면서, 공핍층이 두꺼워지고, 강해진 drain 전계에 의해 source와 channel 사이의 potential barrier가 낮아지는 현상

-> 문턱전압보다 낮은 전압에서도 전류가 흐름(누설 전류)

2) punch through

source와 drain의 공핍영역이 channel보다 하부영역에서 닿으면,

gate 전압에 관계없이 source-drain 사이에서 carrier가 이동하게되고, gate 전압으로 transistor의 동작을 제어하기 어려워진다.

*short channel effect 해결법

DIBL의 sol : drain 전계의 영향이 작도록 설계

ex) FinFET/SOI(silicon on oxide)처럼 게이트 전계가 채널영역을 제어하는 능력이 좋은 tr

punch through의 sol : source-drain 영역에서 공핍층이 증가하는 걸 방지

ex) Halo doping - source/drain 코너부분에 기판 도핑을 높여 공핍영역이 증가하는 걸 방지함

(공핍층의 폭은 도핑농도에 반비례)

이번엔 공핍층에 대해서 더 알아볼 건데 공핍층이란 개념을 제대로 알고가야 나중에 더 공부할 때 고생 안한다 그러는데 그럼 공부 해야지 ㅎㅎ 해보자 공핍층에서의 전계와 전위를 알아보자 그러려면 우선 전하..

'반도체' 카테고리의 다른 글

| [메모리 반도체] DRAM의 구조와 동작원리 (0) | 2023.04.16 |

|---|---|

| [전자회로] differential 회로/current mirror/active load/CMRR (0) | 2023.04.16 |

| [전자회로] short circuit transconductance (0) | 2023.04.14 |

| [전자회로] MOSFET 증폭기 설계 (0) | 2023.04.13 |

| [디지털 집적회로] CMOS inverter의 동작특성 (0) | 2023.04.13 |