| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- FiniteStateMachine

- shortcircuitctransconductance

- 아날로그회로설계

- Flash메모리

- DRAM

- 삼성전자DS

- 회로설계

- 삼성전자인턴

- voltagedoubler

- levelshifter

- 메모리반도체

- combinational

- DRAM의동작특성

- 소신호해석

- 삼성전자대학생인턴

- 따상

- 디램동작원리

- 회로설계취준

- 전자회로

- cmosinverter

- 비휘발성메모리

- 반도체

- DRAM동작원리

- 삼성전자인턴합격

- 차동구조

- 따따상

- nonblocking

- currentmirror

- 디지털집적회로

- 소신호

- Today

- Total

루피덕후의 블로그

[전자회로] differential 회로/current mirror/active load/CMRR 본문

*differential 회로의 필요성

: dc전압에 생기는 ripple 전압이 output에 종종 영향을 주므로,

이 noise(ripple 전압)를 제거하기 위해 differential 회로를 도입함

idea1) 본래의 회로와 생김새와 동작특성이 같은 쌍둥이 회로를 추가해서 ripple 전압을 상쇄함

한계 : rippel전압이 상쇄되지만, gain 또한 상쇄됨

idea2) ripple 전압은 상쇄시키면서, gain을 확보할 수 있는 쌍둥이 회로

두 회로의 input으로 서로의 차가 기준이 되는 differential signal(크기는 같고 위상은 반대)을 인가하면,

gain은 확보하고 . ripple 전압도 상쇄할 수 있다.

* differential 회로의 input 전압은 보통 transformer를 통해 인가된다,

*virtual gnd

differential circuit에서 두 회로의 transconductance(gm)이 같으므로, △Ic 절댓값이 같아

△Ic1 + △Ic2 = 0

공통 소스 단자를 node P라고 할 때,

gm=△Ic/△Vgs임에 따라 △Vp = 0

*small signal gain

diff 회로가 symmetric일 때, diff 회로의 small signal gain(Av) = △(vout1-vout2)/△(vin1-vin2)은

single ended의 gain과 같은 값을 가진다.

따라서 symmetric한 diff회로의 small signal gain은 half circuit(from virtual gnd)을 사용하여 구하면 된다.

*differential circuit의 trade off

공통 emitter나 source단자에 위치하는 tail current가 보통 전류원이므로

biasing이 쉽고 선형성이 확보된다는 장점이 있지만,

두 회로에 의해 전력이 두배 소모되고, area를 많이 차지한다는 단점이 있다.

|

장점

|

단점

|

|

biasing이 쉽다/선형성 확보

|

전력 소모 2배

|

|

voltage swing이 single ended의 2배

(∵differential 회로의 차동 입력은 서로의 차가 전압의 기준이므로) |

area 많이 차지

|

|

noise 제거에 용이

|

|

CMRR(common mode rejection ratio)

=Adm-dm/Acm-dm

차동회로에서 전압이득은 1) △Vout-cm/△Vin-cm 2) △Vout-dm/△Vin-cm 3) △Vout-dm/△Vin-dm

1),2)는 tail current가 non ideal하거나, asymmetric 구조일 때

공통모드의 input전압이 output에 어떠한 영향을 주는지를 나타내는 척도이다.

따라서 차동회로에서는 공통모드 전압을 제거하는 것이 목적이므로

CMRR의 분자인 Adm-dm이 높을 수록, Acm-dm이 낮을수록 CMRR이 좋다고(잡음제거를 잘한다고) 한다.

*CMRR과 OPAMP

ideal한 OPAMP는 입력단자에 들어오는 두 신호의 차를 무한대로 증폭하므로, CMRR값이 무한대이다.

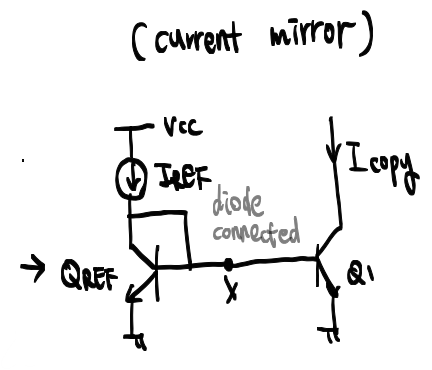

Current mirror

도입 배경 : Vt와 mobility = f(T), 온도에 대한 함수이므로 bjt와 mos 등의 transistor가 온도에 민감하다는 단점이 있다.

collector 전류와 drain 전류가 온도에 영향받지않도록 설계하기 위해, 온도에 따라 그 전류 특성이 바뀌지 않는 reference 전류원의 전류를 복사하는 'Current mirror' 개념이 도입되었다.

reference 전류원는 diode connected 구조로

drain-gate/ collector-base 노드가 묶여있고 drain/collector에 전류원 load를 가지고있다.

이 떄 묶인 노드는 복사될 transistor의 base/gate 노드와 공유되어,

copy 전류가 b-e/g-s에 의해 영향을 받지 않으며, base/gate current가 흐를 통로를 확보한다.

bjt의 경우에는 reference 전류원의 scaling emitter area,

mosfet의 경우에는 reference 전류원의 W/L에 비례하여 I copy가 결정된다.

* current scaling

1) copy tr이 묶여있지 않은경우, 각각의 tr과 reference tr의 size의 비율에 의해 Icopy가 결정됨

2) copy tr이 병렬로 묶여있는 경우, W/L 또는 Q값이 동일하다는 가정하에 copy tr의 갯수에 비례하여 Icopy가 결정된다.

3) reference 전류원이 병렬로 묶어있는 경우 2)와 반대로 copy에는 1/N의 전류가 흐르게 된다.

*current mirror의 장점

: 온도에 따라 변하지않는 전류 값을 얻을 수 있음

/일반적인 정전류원 하나를 배치할 때보다 공간 효율이 더 좋음

differential pair with active load

diffrential 입력으로 single-ended의 출력을 갖는 회로를 구성할 때

한 쪽 회로의 활용도가 낮으며, ripple 전압이 제거할 수 없다는 문제가 발생한다.

이 때 수동소자 대신 active load를 load로 사용하게되면, gain loss와 활용도 문제 없이 ripple 전압을 상쇄시킬 수 있다.

(아래 그림에서는 active load의 일례로 current mirror를 사용, 이 때 회로는 asymmetric이므로 half circuit으로 small signal gain을 구하지 않고 vth-rth개념을 사용하거나 small signal 해석으로 small signal gain을 구한다.)

'반도체' 카테고리의 다른 글

| [메모리 반도체]NAND FLASH의 구조와 동작원리 (0) | 2023.04.17 |

|---|---|

| [메모리 반도체] DRAM의 구조와 동작원리 (0) | 2023.04.16 |

| [전자회로] mosfet I-V curve/channel length modulation/short channel effect (0) | 2023.04.14 |

| [전자회로] short circuit transconductance (0) | 2023.04.14 |

| [전자회로] MOSFET 증폭기 설계 (0) | 2023.04.13 |